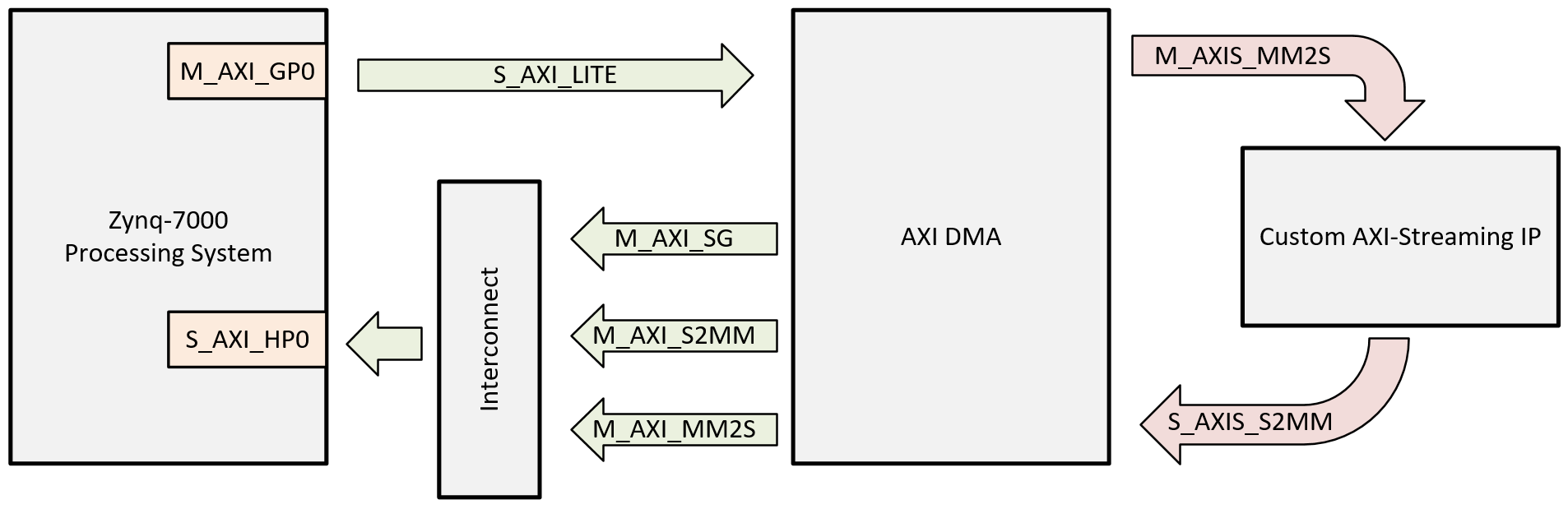

On the effectiveness of accelerating MapReduce functions using the Xilinx Vivado HLS tool | Semantic Scholar

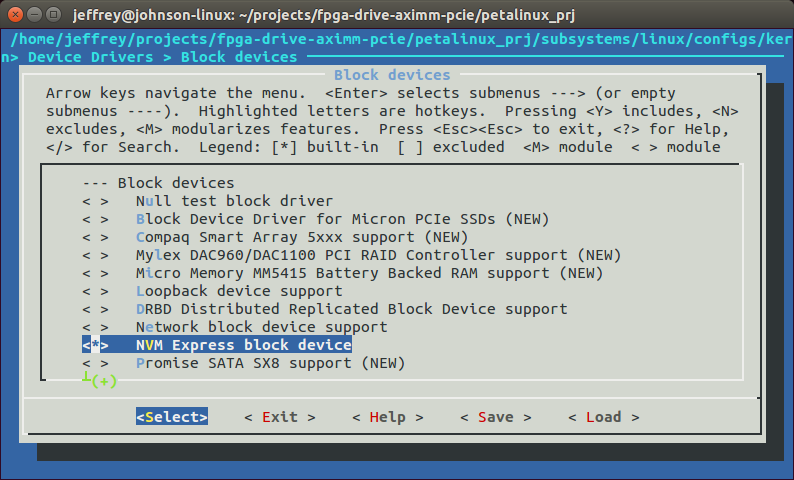

Using DPU-TRD Vivado for zcu104 to reconfigure the hardware design · Issue #746 · Xilinx/Vitis-AI · GitHub

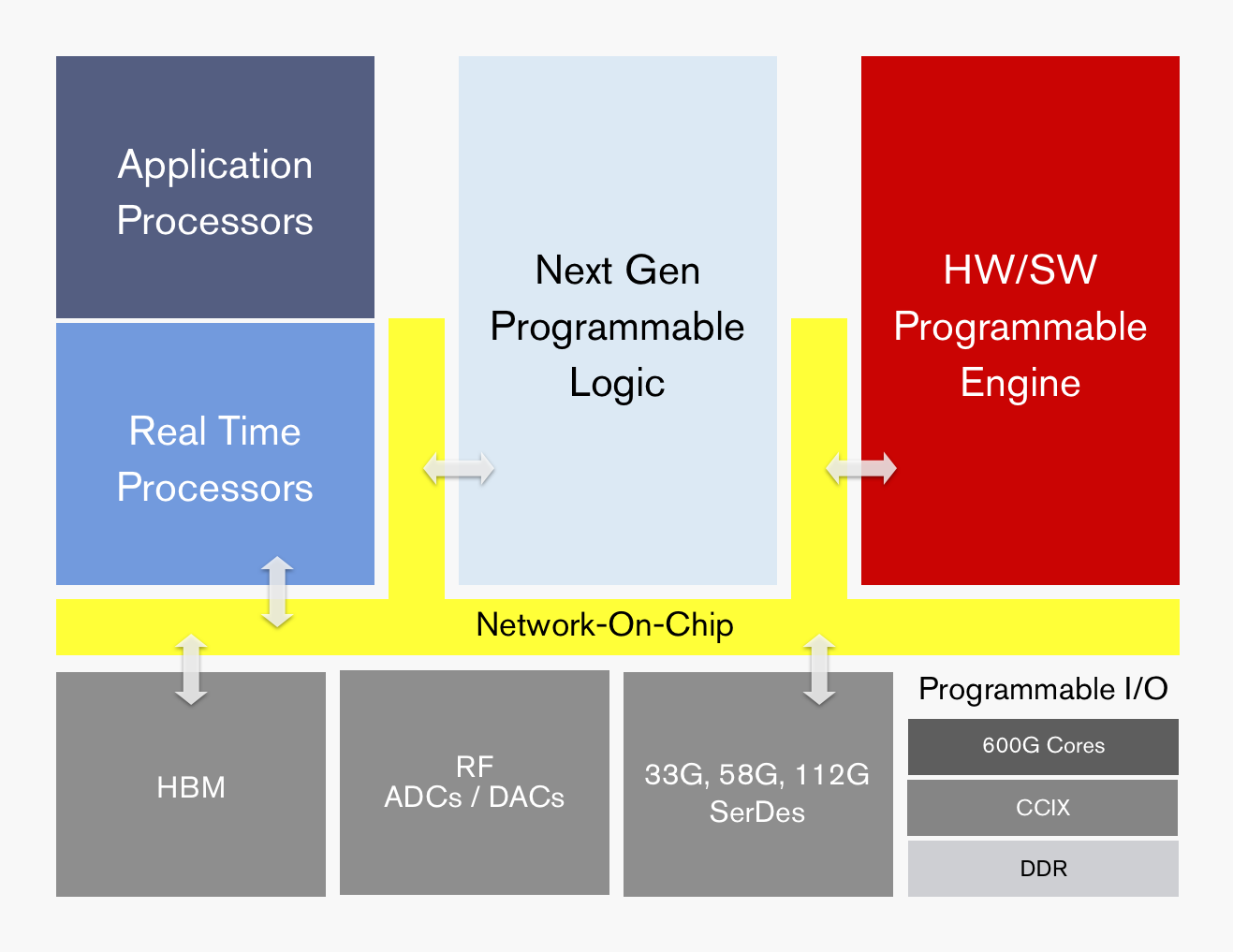

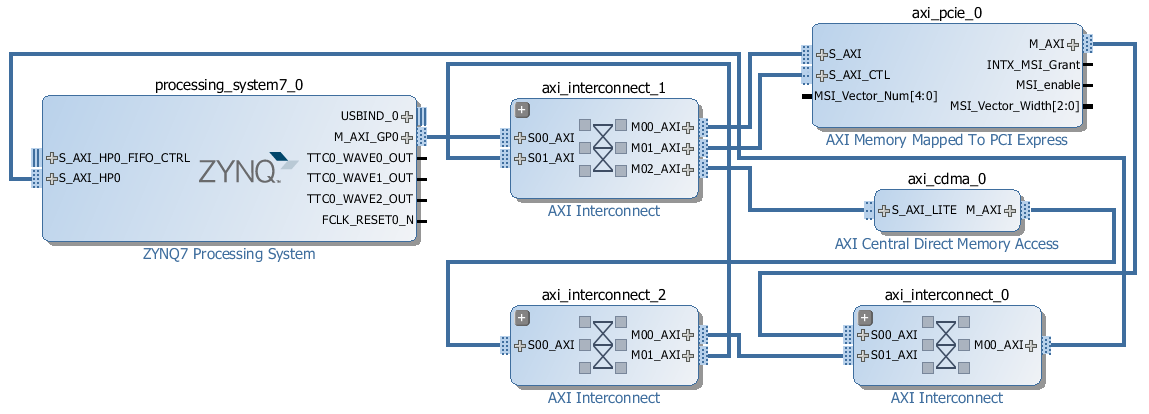

Vivado Design Interface: Enabling CAD-Tool Design for Next Generation Xilinx FPGA Devices | Semantic Scholar